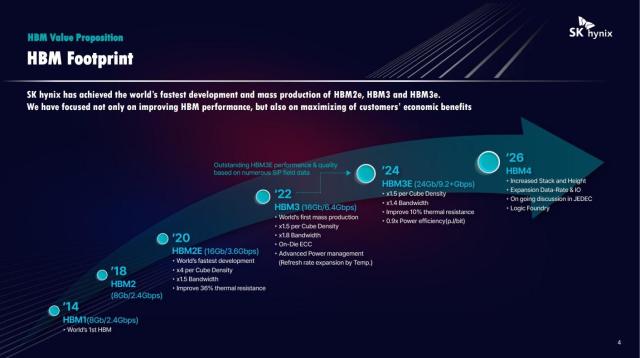

21일 반도체 업계에 따르면 SK하이닉스는 미국 캘리포니아주 새너제이에서 열린 엔비디아 GTC 2024 행사에 참가해 '생성 AI와 슈퍼컴퓨터(HPC)를 위한 5세대 HBM(HBM3E) 가치 제안' 특별 세션을 진행했다. HBM 전문가인 황현 테크리더가 진행한 이번 세션에서 SK하이닉스는 HBM3E 기술과 함께 HBM4 기술 로드맵을 공개했다.

HBM은 여러 개의 칩을 쌓고 위 아래로 데이터 통로(TSV·실리콘 관통전극)를 뚫어 대역폭을 기존 GDDR(그래픽더블데이터레이트메모리) D램보다 크게 향상한 차세대 D램이다. 대역폭은 시간당 전송할 수 있는 데이터 양을 의미한다.

특히 인공지능(AI) 모델을 학습하려면 반도체 코어와 D램이 실시간으로 빠르게 데이터를 주고받아야 하는 만큼 학습용 AI 반도체에는 HBM이 필수로 여겨진다.

수율을 향상하면서 발열을 줄이기 위해 제조 방식(HBM Package)도 '차세대(Advanced) MR-MUF'에서 '하이브리드 본딩'으로 전환한다. 하이브리드 본딩은 칩을 쌓을 때 전기를 통하게 해주는 전도성 돌기(범프)를 없애고 칩을 바로 붙여서 데이터 전송 속도와 적층 효율성을 끌어올리는 기술이다.

기존에는 엔비디아·AMD 등 AI 반도체 기업 중심이었던 HBM 고객도 자율주행차 제조사 등으로 확대하겠다는 포부를 드러냈다. 그만큼 HBM 생산능력(캐파)과 수율 확보에 자신있다는 뜻으로 해석된다.

다만 SK하이닉스 관계자는 이번 발표에서 공개한 HBM4 성능이 확정된 것은 아니라고 강조했다. 엔비디아 등 주요 고객사의 요청에 맞춰 성능이 더 향상될 가능성이 있다는 설명이다. 실제로 3세대 HBM(HBM2E) 이후 HBM D램 성능은 주요 고객인 엔비디아의 요청에 맞춰 향상되는 경우가 잦았다.

삼성전자도 지난 2월 세계 최대 반도체 학술행사인 'ISSCC 2024'에서 HBM4 개발 계획을 알렸다. 이에 따르면 삼성전자 HBM4는 대역폭이 전작보다 66% 늘어난 초당 2TB를 목표로 하며, 쌓는 칩의 수도 16단으로 확대하며 최대 48GB 용량을 지원할 계획이다.

©'5개국어 글로벌 경제신문' 아주경제. 무단전재·재배포 금지

![[르포] 중력 6배에 짓눌려 기절 직전…전투기 조종사 비행환경 적응훈련(영상)](https://image.ajunews.com/content/image/2024/02/29/20240229181518601151_258_161.jpg)