차세대 반도체 패키징(이종 반도체 결합) 공정인 '팬아웃-패널레벨패키징(FO-PLP)' 시장이 급성장할 것이란 예측이 나왔다. 이에 경쟁사보다 일찍 패널레벨패키징 분야 연구·개발을 지속해 온 삼성전자가 반도체 후공정 분야에서 대만 TSMC를 따라잡을 수 있을 것으로 기대된다.

4일 대만 시장조사업체 트렌드포스에 따르면 최근 엔비디아, AMD 등 주요 칩셋 설계사(팹리스)들의 수요가 늘면서 FO-PLP 공정이 파운드리(위탁생산) 업계 화두로 떠오르고 있다. 특히 올해 하반기부터 관련 기술을 활용한 차세대 칩이 본격적으로 대량 양산될 전망이다.

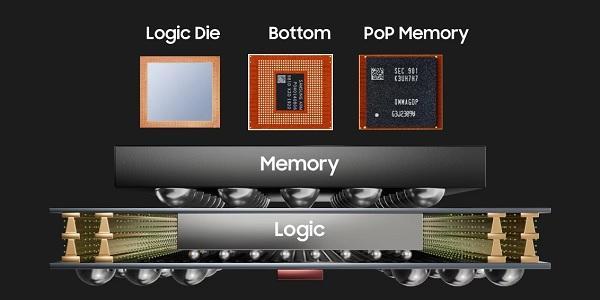

FO-PLP 공정은 기존 반도체 웨이퍼보다 넓은 직사각형 기판으로, 더 많은 칩을 배치해 생산 효율이 높고 비용을 절감할 수 있다. 현재 반도체 패키징 업계 선두인 TSMC '칩 온 웨이퍼 온 서브스트레이트(CoWoS) 공정의 대안으로 주목받고 있다.

그동안 TSMC는 인공지능(AI) 반도체 생산을 위해 독자 개발한 CoWoS 공정을 활용해 왔다. CoWoS는 수평·수직으로 칩과 기판을 연결함으로써 칩의 집적도·속도·성능·공간절약 면에서 우수하다는 평가를 받아왔다. 이런 평가를 토대로 TSMC는 AI 반도체 관련 특허와 물량을 사실상 독점 중이다.

삼성전자도 'H-큐브' 등 독자적인 반도체 패키징 기술을 개발하며 고객 확대에 나섰지만 TSMC만큼 성과를 거두진 못했다.

하지만 엔비디아, AMD, 브로드컴 등 고객사 수요 급증과 CoWoS 공정의 고질적인 문제인 생산 '병목현상'으로 AI 반도체 공급에 차질이 생기면서 TSMC·삼성전자 등 주요 파운드리 업체는 FO-PLP를 비롯한 PLP 분야로 눈을 돌리고 있다.

이는 CoWoS·H-큐브 등 기존 반도체 패키징 공정의 생산능력을 끌어올리면서, FO-PLP 공정을 도입해 나날이 증가하는 AI 반도체 주문량을 소화하겠다는 이원화 생산구조 전략으로 풀이된다.

이에 시장조사업체 욜그룹은 전체 반도체 패키징 시장에서 FO-PLP 점유율이 2022년 2%에서 2028년 8%까지 늘어날 것으로 예측했다.

삼성전자는 앞서 2019년 삼성전기로부터 PLP 사업 부문을 인수해 FO-PLP 공정 연구·개발과 사업화에 박차를 가해왔다. 특히 PLP 공정을 스마트폰용 모바일 칩(AP)에 적용하며 관련 기술력을 키워왔다. 반도체 업계에서는 삼성전자가 PLP 관련 기술만큼은 TSMC를 앞서고 있는 것으로 본다.

지난 3월 주주총회에서 경계현 전 삼성전자 반도체 DS 부문장도 PLP 공정 기술의 필요성을 설명한 바 있다. 그는 "AI 반도체 다이(회로가 형성된 직사각형 조각)는 일반적으로 600㎜ x 600㎜나 800㎜ x 800㎜로 크기 때문에 PLP와 같은 기술이 필요하다"며 "삼성전자도 연구·개발 중이며 고객사들과 협력하고 있다"고 말했다.

실제로 삼성전자는 지난 3일 FO-PLP를 적용한 3나노 2세대 게이트올어라운드(GAA) 공정 기반의 웨어러블용 AP '엑시노스 W1000' 양산 소식을 알리면서 관련 기술력과 수율을 입증하는 데 성공했다. 해당 칩은 삼성전자가 오는 10일 프랑스 파리에서 진행하는 '갤럭시 언팩 2024'에서 발표할 차세대 스마트워치 '갤럭시 워치7 시리즈'에 탑재될 전망이다.

FO-PLP 공정은 모바일, 웨어러블 장치 등 저전력 메모리 집적화 분야 외에도 AI 반도체와 슈퍼컴퓨터(HPC)용 칩 등 고성능 컴퓨팅 분야에도 적용할 수 있는 만큼 향후 삼성전자 파운드리 사업부가 국내외 AI 반도체 팹리스와 미국 빅테크가 개발 중인 AI 반도체를 고객으로 유치할 때 '통합 AI 솔루션'과 함께 핵심 경쟁력으로 작용할 전망이다. 통합 AI 솔루션은 종합반도체기업(IDM)인 삼성전자가 AI 반도체 팹리스들이 필요로 하는 초미세공정·HBM(고대역폭 메모리) D램·반도체 패키징을 턴키로 공급하는 전략이다.

한편 삼성전자는 오는 7월9일 서울 강남구 코엑스에서 '삼성 파운드리 포럼(SFF) 2024'를 개최하고 고객사·파트너사를 대상으로 FO-PLP 기술 진척도를 포함한 통합 AI 솔루션의 강점에 관해 설명할 것으로 알려졌다.

©'5개국어 글로벌 경제신문' 아주경제. 무단전재·재배포 금지

![[르포] 중력 6배에 짓눌려 기절 직전…전투기 조종사 비행환경 적응훈련(영상)](https://image.ajunews.com/content/image/2024/02/29/20240229181518601151_258_161.jpg)